AMD Phenom Preview: Barcelona Desktop Benchmarks

by Anand Lal Shimpi on September 10, 2007 12:03 AM EST- Posted in

- CPUs

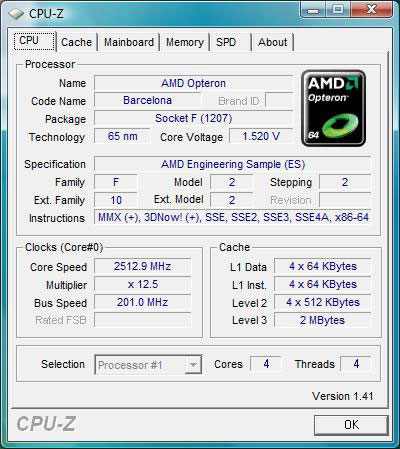

2.0GHz Today, 2.5GHz Tomorrow

At the last minute, AMD informed us that we'd be receiving three sets of Barcelona processors: a pair of 1.9GHz chips, 2.0GHz chips and 2.5GHz chips. The latter won't be shipping until Q4 of this year, but AMD wanted to show that Barcelona is yielding at higher clock speeds and that there is a roadmap going forward.

Barcelona - 1.9GHz

Barcelona - 2.0GHz

To be honest, we expected 2.5GHz by the end of year from AMD, and slightly higher on the desktop but it's good to actually have silicon in hand instead of empty promises or hunches.

AMD taking notes from Intel, hand written clock speeds are in.

With 2.5GHz in hand today, we'd expect Phenom to be at or below 2.6GHz by the end of the year, with 3.0GHz coming sometime in 2008.

70 Comments

View All Comments

MadBoris - Monday, September 10, 2007 - link

hmm, especially if it is only @cas5, as mentioned above.It will be interesting to see if it yields anything more than just a few percent, as to scaling, and if benefits compound per socket.

As to one socket and 4 cores I don't really envision it being that much more than a few percent, but then again, I'm not investing any thought or speculation to try and figure out what will be answered when it actually matters and HW is available.

Major point for me is, being able to OC a q6600($280) to 3.2GHz - 3.4GHz on air is going to be real stiff competition for AMD's Phenom, as to my purchasing decisions, which is all I am concerned about mainly.

Also I believe all peoples talk about "true" quad is going to fall a bit flat for the majority of applications/games in real world comparisons with Kentsfield. Because already anyone that is interested to research it can see that the cache/bus penalties in scaling from 2 to 4 cores is basically nonexistent on applications that actually 'fully leverage' all 4 cores. Some apps will benefit, but I expect this to come to light before long and people will see that the penalty of 2 cores in one (Intel Quad), was more speculation, than actual reality, for 'most' consumer applications and games.

I do like AMD's advances but we seriously need more frequency, CPI cannot be overlooked.

duploxxx - Monday, September 10, 2007 - link

if AMD is already able to show multiple phenom systems on 3.0GHZ without dditional cooling (just boxed heatpipe cooler) then i wouldn't be too worried about oc performance of k10ilkhan - Monday, September 10, 2007 - link

15% over K8 is not going to be enough if it launches at (or at least doesn't overclock easily to) 3.2Ghz. At the 2.5 indicated here, yorkfield@3.2+ is going to eat agena for lunch, while being more profitable for intel than agena can hope to be for AMD.Pity.

JackPack - Monday, September 10, 2007 - link

Based on these numbers, consumers are likely going to stick with Intel quads.Clock for clock, Kentsfield was often >30% faster than Quad FX. Barcelona being 15% faster than K8 is reasonable but it's clearly not going to touch Penryn/Yorkfield.

duploxxx - Monday, September 10, 2007 - link

Alltough it is nice to see what anand tried to put here on electronic paper. I can't be compared to the real phenom in a few months.If you want to know why, check Anand's memory review of a year a go and check how well k8 and also k10 is scaling with better/faster memory.

in a barcelona rig you have reg 667@cas5.

so people who are already making conclusions on these benches, one reply: too early.

JackPack - Monday, September 10, 2007 - link

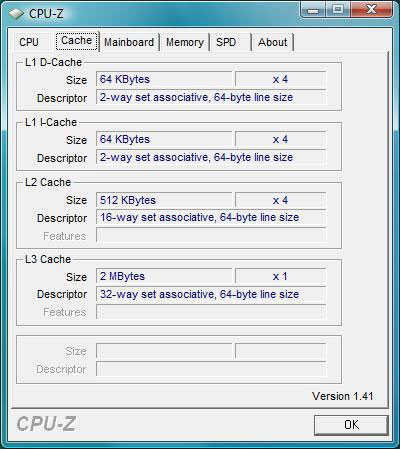

This isn't K8 though. The L3 in Barcelona is going to make it less sensitive to memory bandwidth and latency.Regs - Monday, September 10, 2007 - link

Memory hits and misses (latency) have nothing to do with the L3. The L3 is there as a buffer for the information being proportion to the 4 cores.JackPack - Monday, September 10, 2007 - link

Look up the term "memory hierarchy."Regs - Tuesday, September 11, 2007 - link

what do you think pulls the data into the L3? God?JackPack - Tuesday, September 11, 2007 - link

It's called prefetching. The data is in the L3 before the CPU needs it, reducing memory traffic and latency.Not only that, but Barcelona has a L3 latency of 20ns. To get data from the main memory, it has to go through all levels of cache. When you look at the cumulative latency of the memory hierarchy, the one or two cycle penalty of RDDR2 is trivial.