Codename Mania

We're about to get into a discussion of two new CPUs cores, both due in the 2009 time frame and we'd like to apologize in advance for the sheer number of code names that may be thrown at you. In the past two days we've heard AMD tell us about the following projects:- Bulldozer

- Bobcat

- Falcon

- Sandtiger

- Shanghai

- Predator

- Budapest

- Spider

- Hardcastle

- Pinwheel

- Cartwheel

Many of these codenames refer to platforms including other codenames; understanding the architecture is honestly easier than understanding the nomenclature, which I believe is bad. We've done our best to organize it all in an easy to understand fashion, so please bear with us.

New CPUs

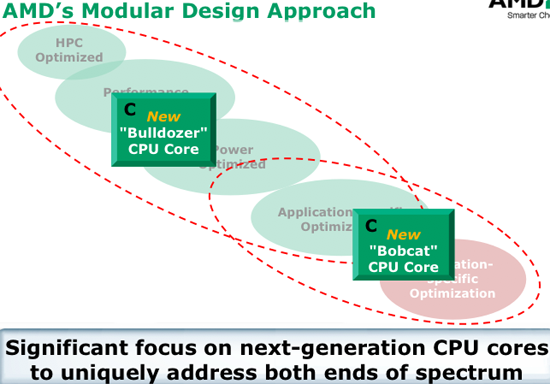

AMD and Intel agree on a lot these days; the 64-bit debate is over, Intel has already committed to bringing an on-die memory controller to market with Nehalem and both companies agree that to address the ultra low power market, you need a new architecture.The rule of thumb is that a single microarchitecture can cover about an order of magnitude of thermal targets, anything higher or lower and you need to look at a different architecture for maximum performance-per-watt efficiency.

AMD divides the market into two spaces: devices that have a TDP of 10 - 100W and devices that are in the 1 - 10W range. AMD has two new CPU cores that it is announcing today: Bulldozer and Bobcat, both due in 2009. Bulldozer addresses the 10 - 100W segment (much like the current K8 and Core based processors do), while Bobcat is designed for the 1 - 10W portion of the market.

Bulldozer

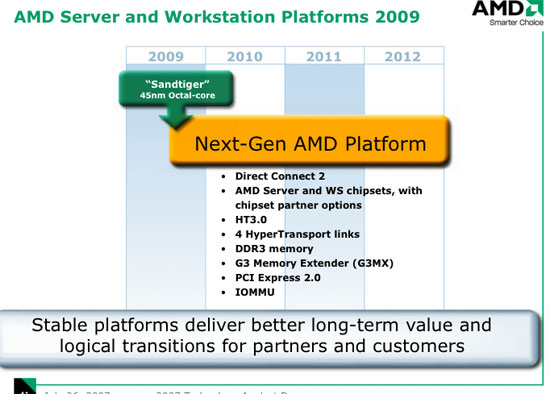

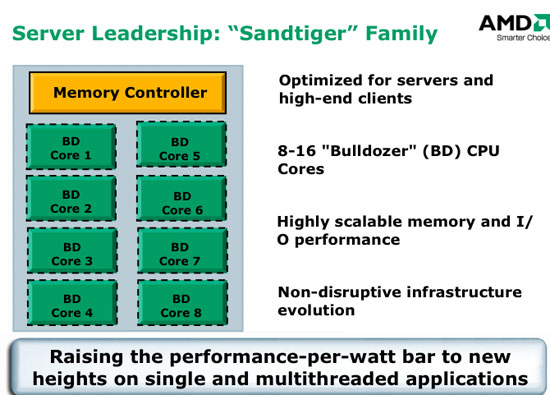

Due out in the first half of 2009, AMD's Bulldozer core is the true revolutionary successor to the K8 architecture. While Barcelona and Shanghai are both evolutionary improvements to the current core, Bulldozer is the first ground-up redesign since the K7.Bulldozer will require a brand new socket for two reasons: it will support a new version of AMD's Direct Connect architecture (and Hyper Transport), and it will also support DDR3. Both of these changes dramatically alter the pinout of the CPU, thus making Bulldozer the next core to not be backwards compatible with current motherboards. Once again, AMD is giving us a nice roadmap for obsolescence, which its customers have always appreciated.

Details on Bulldozer are still limited, but here's a quick list of what we know about the architecture

- Not VLIW, still OoO superscalar architecture

- Deeper pipeline than Barcelona/Shanghai

- New x86 instructions targeted at HPC and "media processing"

- increased computational density

- increased flow control capability

- extend SIMD capability targeted specifically at media data types - Hyper Transport 3 will be supported

- The chip will feature 4 HT3 links

- DDR3 support - G3MX Memory Technology

- PCIe 2.0 - IOMMU (Hardware Accelerated I/O Virtualization)

A deeper pipeline than present-day architectures means we are looking at higher clock speeds, and AMD was quick to point out that there is no dramatic change in the approach to microprocessor design with Bulldozer - it's still the same type of out of order, superscalar architecture as its predecessors and not an Itanium-like design.

Extending the x86 instruction set once more only makes sense as the usage model for general purpose microprocessors becomes more demanding. AMD wouldn't be any more specific about the types of instructions we are likely to see in Bulldozer other than they would be HPC and media processing focused.

Bulldozer's connectivity will be improved, supporting up to four HT3 links per processor (up from 3 HT links in present day CPUs). With four HT3 links you can expect to see some pretty robust multi-socket configurations built around Bulldozer cores in the server/HPC markets.

Why is PCI Express 2.0 listed as a feature of the Bulldozer core? Well, some implementations of the core (think Fusion) will actually have on-die PCI Express 2.0 controllers. These CPUs will be particularly interesting for small form factor devices, because the only additional chip you will need is a South Bridge.

31 Comments

View All Comments

flashbacck - Thursday, July 26, 2007 - link

Whoever decided those acronyms were necessary should be fired.fzkl - Thursday, July 26, 2007 - link

Like mentioned, the obvious great benefit of having low power x86 chips on mobile phones is the software aspect. PC applications can now run on phones reducing aspirin needs for developers. However, what does this mean in terms of security? Can we see mobile phones needing frequent patches, antivirus, firewalls like in the case of desktops?If this were to be the case we would have successfully made a simple device like the mobile phone(in usage terms) a high maintenance product which a layman might have trouble with.

sheh - Thursday, July 26, 2007 - link

x86 doesn't imply any OS or API. Linux, which is commonly used today on all kinds of devices, can work just as well on x86. Conversely, nothing prevents virus writers from writing viruses for Linux running phones.beyoku - Thursday, July 26, 2007 - link

what happened? Was this article recelty pulled off or something?NDA???

Guuts - Thursday, July 26, 2007 - link

Looks to me like he's trying to get the images working...erwos - Thursday, July 26, 2007 - link

Fusion looks like it'll be a fantastic chip for UMPCs and laptops. Hopefully they'll manage to squeeze more than CPU one core on there, too. Bobcat looks similarly fun - x86 phones! VIA was also discussing this idea, and I could really go for it.That said, AMD is really under-delivering with Barcelona - I suspect the next few years will be pretty rough. Intel has set a low ceiling price for the Barcelonas ($270 - same as the Q6600), and that's not going to be good for AMD's margins.

mlau - Thursday, July 26, 2007 - link

Embedded is ruled by ARM, Freescale, mips and sh derivates; amd and intel are going to have a tough time getting a super-ugly system like pc-x86 (with it's

legacy baggages "bios", "acpi" [you know, the stuff windows requires to run], ...) into that space.

Spoelie - Friday, July 27, 2007 - link

you do not need to have those things to run an x86 cpuloot at EFI for example, in use by apple on their x86 based macs = no more bios.

qpwoei - Sunday, July 29, 2007 - link

The real problem with x86 is that it's inherently not power efficient. To get good x86 performance requires lots of transistors and lots of power due to complex decoders and schedulers. A much simpler architecture like ARM requires very few transistors to run efficiently (at the expense of slightly less compact executable code), and is much more suited for battery-powered devices.Not to say that there won't be x86-powered devices in the future, just that I don't expect them to really gain much of a foothold in any place where battery life is important (eg: phones).

ss284 - Thursday, July 26, 2007 - link

Return of the Jedi